# Translating SMALL Programs to FPGA Configurations

Ying Shen & Theodore S. Norvell Memorial University of Newfoundland NECEC 1999

## SMALL

### SMALL is ...

- An imperative programming language

- *Synchronous* and *parallel*

- A low level language compared to C

- A high level language compared to VHDL

- Intended for hardware design

### The SMALL implementation

- From program to hardware at a keypress.

- Short design cycles

- Reasonable efficiency

- Thesis:

- \* hardware is becoming very cheap

- \* hardware is programmed more than manufactured

- \* programmed hardware is getting faster faster

Design costs will dominate.

## **The elements of SMALL**

#### **Types and Expressions**

- Booleans Logic expressions

- N-Dimensional Arrays Arithmetic & APLish expressions

#### Entities

- Registers Record values

- Signals Transfer values to parallel statements.

#### **Statements**

| $r \leftarrow Exp$                                                           |

|------------------------------------------------------------------------------|

| s!Exp                                                                        |

| tick                                                                         |

| $\mathbf{par} \ S \parallel T \parallel U \mathbf{rap}$                      |

| S T U                                                                        |

| $\mathbf{if} \operatorname{Exp} \mathbf{then} S \mathbf{else} T \mathbf{fi}$ |

| $\mathbf{while} Exp \mathbf{do} S \mathbf{od}$                               |

| repeat S until Exp                                                           |

|                                                                              |

Translating SMALL Programs to FPGA Configurations

## **Timing semantics**

#### Time passes only

- at *tick* statements

- after loop iterations

- for parallel process waiting for another to terminate.

|                     | $s \mid 10$ as 4 bits |

|---------------------|-----------------------|

|                     | t ! s - u             |

| is identical to     |                       |

|                     | t ! s - u             |

|                     | $s \mid 10$ as 4 bits |

| But                 |                       |

|                     |                       |

|                     | $s \mid 10$ as 4 bits |

|                     | tick                  |

|                     | t ! s - u             |

| is NOT identical to |                       |

|                     | t ! s - u             |

|                     | tick                  |

|                     | $s \mid 10$ as 4 bits |

|                     |                       |

Translating SMALL Programs to FPGA Configurations

## Implementations

- Simulator for debugging of designs

- Compiler for hardware implementation

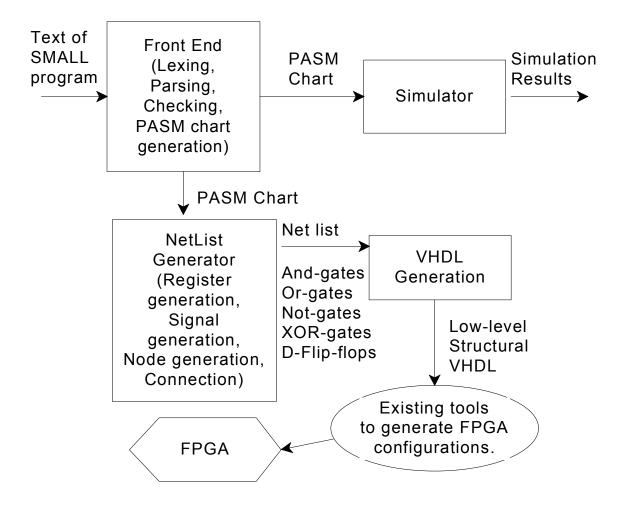

### **Implementation block diagram**

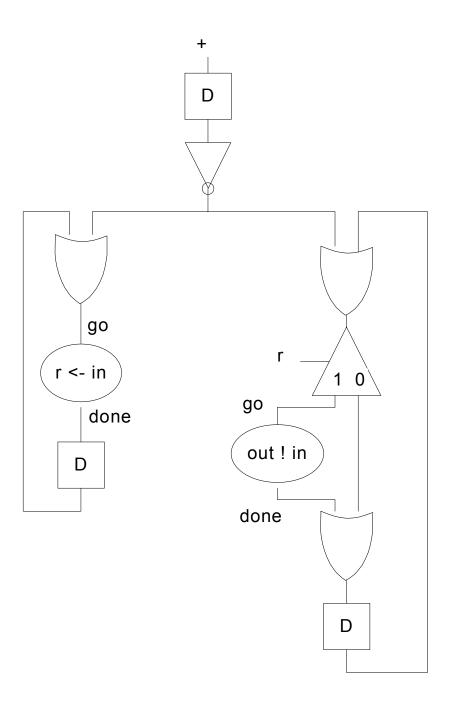

### Parallel Algorithmic State Machine Charts (PASM Charts)

A state-machine representation for control flow.

#### **Example SMALL program**

```

\begin{array}{c} \textbf{global sig } in : bool \\ \textbf{global sig } out : bool \\ \textbf{reg } r : bool \\ \textbf{par} \\ & \textbf{while } true \\ \textbf{do } r \leftarrow in \\ \textbf{od} \\ \parallel \\ \textbf{while } true \\ \textbf{do if } r \\ \textbf{then } out ! in \\ \textbf{fi} \\ \textbf{od} \\ \textbf{rap} \\ \end{array}

```

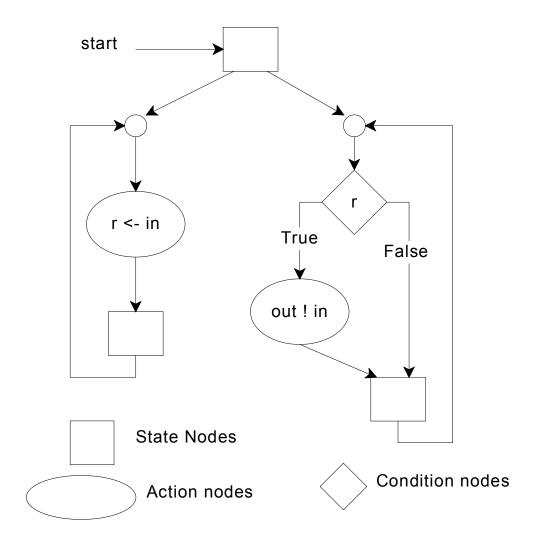

#### **Example PASM Chart**

The state is represented by a set of active state-nodes. Nodes reachable from an active state-node are executed. Then all state nodes reachable from an active state-node become active.

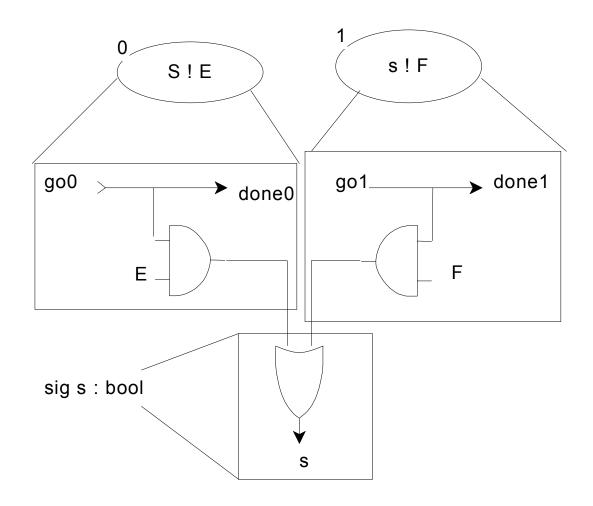

### **Translation of signals and asserts**

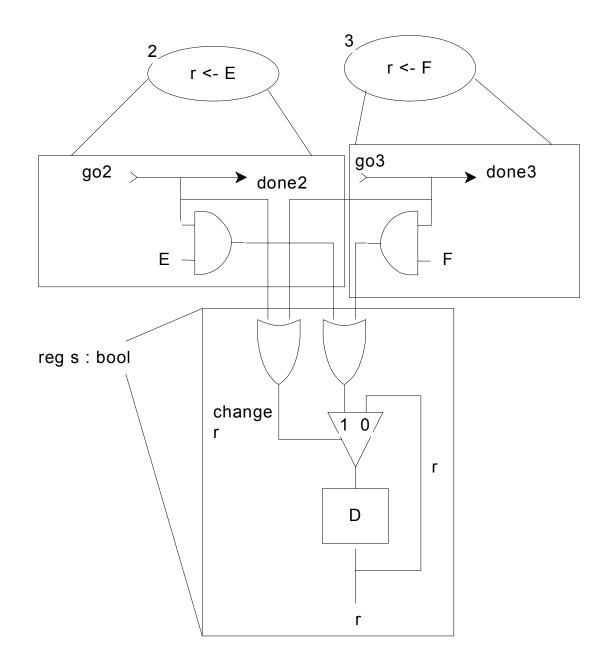

### **Registers and assignments**

### **Dealing with Control State**

# Optimization

- Dead device and wire elimination

- \* Deadwood is removed

- Constant folding and propagation

- \* Ground and power inputs eliminated

- Common subcircuit elimination

- \* Two devices with the same inputs

- PASM chart level not yet done

- \* Sharing of nodes and expressions

Translating SMALL Programs to FPGA Configurations

## **Future Directions**

- Language improvements

- \* Asynchronous communication.

- \* Module system and separate compilation

- \* Higher level types

- \* User defined types

- Compiler improvements

- \* Speed and Space

- \* More optimization resource sharing.

- Industry involvement