Memorial University of Newfoundland

## Engineering 4862 MICROPROCESSORS Assignment 5 Solution

**Please note:** Part A is due next Friday (July 20) and Part B is due on July 27. The last question is a bonus question that worth 2 Marks of the final total mark (Equivalent to the mark of one assignment)

### -- Part A --

0. What control byte will configure an 8255A PPI such that Ports A & B are input, and Port C is output? Solution: From the PPI data sheet, we can get

| Bit              | Value | Reason                |

|------------------|-------|-----------------------|

| $\mathbf{D}_7$   | 1     | mode set              |

| $D_6D_5$         | 00    | Mode 0 for Group A    |

| $D_4$            | 1     | Port A Input          |

| $D_3$            | 0     | Port C (upper) Output |

| $D_2$            | 0     | Mode 0 fro Group B    |

| $\mathbf{D}_1$   | 1     | Port B input          |

| $\mathbf{D}_{0}$ | 0     | Port C (lower) output |

Control byte 1001 0010 (92H)

1. Sketch a diagram of an address decoder for an 8-bit input port. The assembly language instruction IN AL, 94h should fetch a byte from the port. There should be no more than 1024 mirror images, and it should not interfere with operation of I/O ports at 0010h and 0037h.

Solution: Next page

2. What is the advantage and penalty of multiplexing and demultiplexing the address/data in the 8088/86 CPUs?

Solution:

It uses less pins and consequently has a smaller package. But it takes longer time because data and address need to be demultiplexed.

**3.** When the input signal RESET in the 8088/86 is activated, what are the contents of the CS and IP register? Why ROM is always arranged to the high/upper end of the memory map (closer to the FFFFFH) for Intel 80x86 serial microprocessors?

Solution:

After reset, for 8086/88, CS=FFFFH, IP=0000H, that gives a physical address FFFF0H. That is where the reset vector is stored. CPU will always go to that address to fetch the first instruction. Because at the time, nothing has been loaded to the RAM, so we have to arrange a ROM to cover that location. Usually, we arrange the ROM from the highest address FFFFFH downward and make the address continuous.

\* 8-bit input port with address 00094h \* Max 1024 mirror images .. max 10 unused address lines \* All I/o addresses only use 16 address lines \* Cannot interfere with ports at 00010h and 00037h A.5 A. New Port (942) 0000 0000 1001 0100 Existing Ports (10h) 0000 0000 0001 0000 (372) 0000 0000 0011 0111 We need to use at least 6 lines, such that we can select the new port, but not the existing ports. For example, choosing lines A10-A15 is a very poor choice. For all three ports, these lines have the value zero. There is way to differentiate each port. ho So Choose 6 lines that have different values for each port. Lines Ao-s will work fine. As Ay Az Az A, Ao 0 1 0 1 0 0 So one possibility for decoding is to use a 3×8 decoder. A A. Α, B C A2 ----A3 \_\_\_\_ E. IOSEL Αs E. A4 Ez

NOTE!

Any address which fits the following pattern is valid: Any XXXX XXXX XX01 0100 Thus port 14 h will also access the same input port. That is okay joo long as port 94h works (it does), the solution meets the specification.

These are many different correct solutions.

y7 \$

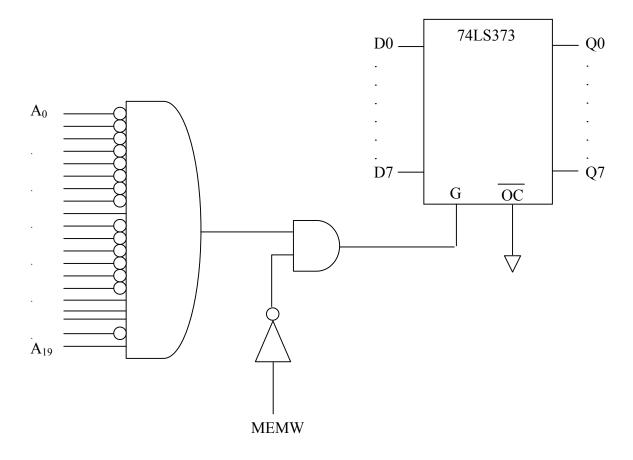

**4.** Show the logical design of "MOV [0100], AL" for memory mapped I/O using AND and Inverter gates and a 74LS373 latch. Assume that DS=B800H.

# The PA=B8000+0100 = B8100H. It use memory mapped I/O so MEMR or MEMW is used. Because we move data to the memory, therefore, MEMW is used.

### -- Part B --

**5.** Calculate, using execution times, the total time required by the following program. Assume the program is running on a system with 5-MHz 8086 microprocessor (with the help of Intel User Manual).

MOV AX, 0000h MOV SI, 0000h MOV CX, 8000h OUTER: MOV DX, CX MOV [SI], AX ADD SI, 2 MOV CX, 0FFFFh INNER: LOOP INNER MOV CX, DX LOOP OUTER

INSTRUCTION CLOCKS 4 Mov AX, ooooh Mou SI, 0000h 4 Mov CX, 8000h 4 OUTER: MOV DX, CX Z 9+EA = 9+5=14 (SI is even) MOV [SI], AX ADD ST, 2 4 MOV CX, OFFFFh 4 SIT if jump (S if no jump INNER: LOOP INNER Z SIT it jump (S it no jump MOV CK, DX LOOP OUTER INNER LOOP CLOCKS : CI = FFFFh × 17 +5 = 65535 ×17 +5 = 1 114 100 OUTER LOOP Clocks: Co = 8000h × 2+14+4+4+2+17+Cz]+5 = 32768 × (1114143)+S = 36 508 237 829 TOTAL = Co+ 4+4+4 = 36 508 237 831 clocks ... Total Time = clocks × period of one clock 5 SMHz = 200 ns = clocks / frequency of clock = 7301.65 seconds = 2 hours 1 minute 41.65 seconds. Note that simply using the time for the immerloop x # of outerloops is accurate to within half a second, and would be acceptable: 8000h × FFFFh × 17 × 200ns = 7301.3 Sec

**6.** Repeat the previous question for a system with a 4.77-MHz 8088 microprocessor. (Only recalculate values that change.)

There are two differences: one is due to uPro used (8088) and the other is due to clockspeed (8088) and the

7. Is it possible to create an 8086-based computer system with one 32KB (8-bit wide) RAM device and one 16KB (8-bit wide) RAM device? Explain.

An 8086-based system uses separate even & odd memory banks, This means that all memory cells that are accessed with even 20-bit addresses are grouped together. Likewise for odd addresses.

Because these addresses are interleaved, it makes no sense to have a range of even addressed memory cells without the corresponding range of odd addressed cells. A standard, single RAM IC can not be used for both banks because it only has an eight-bit dota path.

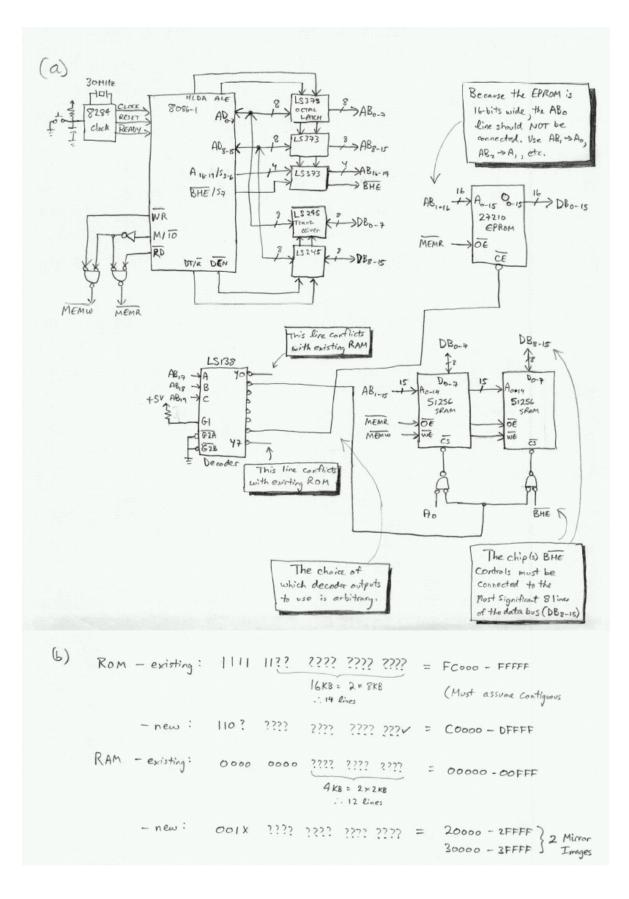

So the given chips do not allow for a feasible 8086-based system. 32KB 16KB 8. An 8086-1 microprocessor based system operating in minimum mode at its maximum speed already includes 4 kilobytes of RAM (two 2K x 8 devices) and 16 kilobytes of EPROM (two 8K x 8 devices), which are mapped in appropriate locations with no mirror images. This system needs to be expanded by adding two 51256S-10 SRAM devices and one 27210-200V10 EPROM device. A new address decoder should be added which would cater to the expansion devices; the most significant three address lines with one 74LS138 should be used for this purpose.

In the Intel 8086/8088 User's Manual (the BlackBook...), the timing requirements for the <u>8086-1</u> is given in the middle columns on pages 6-78 and 6-79 for a <u>Minimum</u> mode system. The first entry, Terer, is the clock cycle period: 100ns \$10 MHz, 500ns \$2 MHz. Thus the maximum speed is Terer = 100ns, for a frequency of 10 MHz.

**a.** Assuming that the data lines needs to be buffered, sketch a circuit diagram illustrating the interface between the CPU and the expansion memory. Show all the connections to the pins of the memory devices; include latches and all the necessary TTL devices. The existing memory devices (4K RAM and 16K ROM) and their address decoders **need not** be included in your diagram.

### Diagram see next page.

**b.** List the address ranges (for both ROM and RWM) corresponding to all memory devices in the system – existing as well as additional devices. List all mirror images.

**c.** Sketch the memory map of the system – including the existing as well as newly added memory – and clearly indicate all mirror images.

**d.** Consider the address line A13. Find out the additional load – current as well as capacitance load – placed on this line due to the expansion. Which device should be capable of driving this additional load?

e. Determine the number of wait states required to interface the (i) SRAM and the (ii) EPROM. Suggested propagation delays are: decoder ~40ns, latch ~30ns, buffer ~25ns, transceiver ~30ns, and each logic gate ~10ns.

**f.** Assume that the O4\* output line of the decoder in your design is used for selecting a pair of memory mapped 8255 PPI devices. Assume also that Port A in both these devices have been configured as input, thus obtaining a 16-bit input port. What address(es) should be used to access this 16-bit port?

**g.** Write a program that will read the contents of this port at a known sampling rate, and store the acquired information in an array located in the expansion RAM; 100 samples are required to be collected. Hint: use the extra segment for the RAM.

**h.** Suppose that the rate at which samples are collected is not pre-determined, but depends on the speed of the input device connected to the 8255. Therefore, you cannot simply write a delay routine to determine when to collect input samples. What hardware/software solution would you recommend to solve this problem? That is, how will you use the 8255 device in this case?

CODEL ENDS EXTRAL SEGMENT Arcl DW 100 DUP(?) EXTRAL ENDS

- (h) The 8255 provides handshaking capabilities which would be useful in this case. The PPI should be configured so that Port A is operating in <u>Model</u> as an input Port. PC4 is a strobe signal from the input device. When a value is received, the PPI can intervpt the CPU and provide the input value.