# **ENGR 5865 DIGITAL SYSTEMS**

## ModelSim Tutorial Manual

## January 22, 2007

#### • Introduction

ModelSim is a CAD tool widely used in the industry for hardware design. This document describes how to edit/add, compile and simulate VHDL code by using ModelSim software. The example code for this tutorial is a simple counter without testbench but setting the values of selected input signals manually in the waveform. Normally, a complete project should include a testbench for each module to instantiate the entity under test, and to initialize the input signals to the module. You may feel like creating your own testbench and simulate it after you complete this tutorial.

#### • Create a Project

In the file menu, choose File -> New -> Project This will bring up the following window:

| Project Name           |    |         |

|------------------------|----|---------|

| tutorial               |    |         |

| Project Location       |    |         |

| D:/My Designs/tutorial |    | Browse. |

| Default Library Nam    | ie |         |

| work                   |    |         |

Put the project in your preferred directory. Leave *work* as the default library name.

## • Edit and Compile the Code

To edit VHDL files, you may use the editor provided by ModelSim, or any external code editors such as Windows Notepad, which is normally faster and more stable than ModelSim text editor. ModelSim can also understand DOS and UNIX coded text files.

If you would prefer the VHDL syntax coloring of ModelSim editor, then you can edit/add a VHDL file by choosing:

File -> Add to Project -> New File..., or

```

File -> Add to Project -> Existing File...

If it is a new file, then create a file name such as "counter.vhd". Edit it as below:

entity counter is

port (count : buffer bit_vector(8 downto 1); -- the most significant bit is

-- buffer (8)

clk

: in bit;

reset : in bit);

end:

architecture only of counter is

constant tpd_reset_to_count : time := 10 ns;

constant tpd_clk_to_count

: time := 5 ns;

function increment(val : bit_vector) return bit_vector

is

-- normalize the indexing

alias input : bit_vector(val'length downto 1) is val;

variable result : bit_vector(input'range) := input;

variable carry : bit := '1';

begin

for i in input'low to input'high loop

result(i) := input(i) xor carry;

carry := input(i) and carry;

exit when carry = '0';

end loop;

return result;

end increment;

begin

ctr:

process(clk, reset)

begin

if (reset = '1') then

if reset'event then

count <= (others => '0') after tpd_reset_to_count;

end if;

elsif clk'event and (clk = '1') then

count <= increment(count) after tpd_clk_to_count;

end if;

end process;

```

```

end only;

```

After you save it, the workspace window will be like this:

| <b>M</b> ∎odelSi∎ SE PLUS                           | 6.0            |       |                  |                           |          |          |

|-----------------------------------------------------|----------------|-------|------------------|---------------------------|----------|----------|

| <u>F</u> ile <u>E</u> dit <u>V</u> iew F <u>o</u> r | mat <u>C</u> o | mpile | <u>S</u> imulate | <u>A</u> dd <u>T</u> ools | Window   | Help     |

| Contains:                                           |                | ] ]   | ] 🗋 🖻            | ; 🛛 🕹   🖁                 | Ķ. 🕅 🖆   | <u> </u> |

| Workspace 💳 🗄 🖻 🕱                                   |                |       |                  |                           |          |          |

| 🔻 Name                                              | Status         | Туре  | Order            | Modified                  |          |          |

| ਿਸ਼ੇ counter.vhd                                    | ?              | VHDL  | 0                | 01/22/07                  | 09:19:28 | РМ       |

Highlight the file to activate the "compile" button on the toolbar:

|                                                                                                                                               | "compile" |

|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| ModelSim SE PLUS 6.0                                                                                                                          | button    |

| <u>F</u> ile <u>E</u> dit <u>V</u> iew F <u>o</u> rmat <u>C</u> ompile <u>S</u> imulate <u>A</u> dd <u>T</u> ools <u>W</u> indow <u>H</u> elp |           |

| Contains: 🔽 🧷 🗋 😂 🐺 🍜 🛛 🕹 🛍 🕰 🖄 🖄 🏟 🏶 🕮 💭 🖄 🗍 🚸 🎬 👰 🔀                                                                                         |           |

| Workspace : Real Real Real Real Real Real Real Real                                                                                           |           |

| Name Status Type Order Modified In #                                                                                                          |           |

| vi counter.vhd ? VHDL 0 01/22/07 09:19:28 PM 1 library IEEE;                                                                                  |           |

| 2 use IEEE.STD_LOGIC_1164.A                                                                                                                   |           |

| 3 use IEEE.STD_LOGIC_ARITH.                                                                                                                   |           |

| 4 use IEEE.STD_LOGIC_UNSIGN                                                                                                                   |           |

| 5                                                                                                                                             |           |

If there is no error in the file, the transcript window at the bottom will show:

| Transcript :                             |

|------------------------------------------|

| # Compile of counter.vhd was successful. |

| ModelSim>                                |

# • Run the Simulation and View the Waveform

With the file status being changed in the workspace after compilation, you can press the "simulate" button to activate the simulation process:

|                                                              | "simulate" |

|--------------------------------------------------------------|------------|

| MBodelSim SE PLUS 6.0                                        | button     |

| File Edit View Format Compile Simulate Add Tools Window Melp |            |

| Contains: 🔽 🧳 🗋 😂 🖉 🎒 🛍 🖄 🖄 🛤 🗱 🖄                            | 🖉 🖽 💭 🐹    |

| Workspace 🔤 🖬 🛋 📓 counter.vhd                                |            |

| Vame Status Type Order Modified In #                         |            |

| vm counter.vhd ✔ VHDL 0 01/22/07 1 library IEEE;             |            |

This will bring up the following window:

| Design VHDL Verilog Libraria            | · · ·   |                                   |

|-----------------------------------------|---------|-----------------------------------|

| Name                                    | Туре    | Path                              |

| □- <b>∭</b> work                        | Library | work                              |

| E counter                               | Entity  | D:/My Designs/tutorial/counter.vi |

| ⊕-,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,  | Library | \$MODEL_TECH77vital2000           |

| 🕀 📶 ieee                                | Library | \$MODEL_TECH//ieee                |

|                                         | Library | \$MODEL_TECH77modelsim_lib        |

| ⊞- <mark>∭</mark> std                   | Library | \$MODEL_TECH//std                 |

| ⊞–∰_ std_developerskit                  | Library | \$MODEL_TECH//std_develope        |

|                                         | Library | \$MODEL_TECH77synopsys 👘          |

| - ili                                   | 1.3     | ANODEL TECHY AL-2-                |

| •                                       |         |                                   |

| Design Unit(s)                          |         | Resolution                        |

| work.counter                            |         | default 💌                         |

| 0-1-1-1-1-1-1-1-1-1-1-1-1-1-1-1-1-1-1-1 |         |                                   |

| Optimization                            |         |                                   |

| Enable optimization                     |         | Optimization Options              |

Choose *counter* in the library *work*, and press OK. Then, the workspace switches to the simulation window by itself:

| Workspace 💳       | + a ×         |

|-------------------|---------------|

| Instance          | Design        |

| 🖃 🗐 counter       | counte        |

| L_ ctr            | counte        |

| 🗾 standard        | standa        |

|                   |               |

|                   |               |

|                   |               |

|                   |               |

|                   |               |

|                   |               |

|                   |               |

|                   |               |

| ,                 |               |

|                   | •             |

| Project 🕕 Library | 🔊 sim 🖾 Files |

Now, you can add selected signals to the waveform.

Select View -> Debug Windows -> Objects

This will bring up a signals window that looks like this:

| MedelSim SE PLUS 6.0                                              |                     |                          |                       |          |                           |            |

|-------------------------------------------------------------------|---------------------|--------------------------|-----------------------|----------|---------------------------|------------|

| <u>F</u> ile <u>E</u> dit <u>V</u> iew F <u>o</u> rmat <u>C</u> o | mpile <u>S</u> imul | ate <u>A</u> dd <u>1</u> | ools <u>W</u> indow   | Help     |                           |            |

| Contains:                                                         |                     | ) 🗲 🔛 á                  | 5   X 🖻 🍘             | *2:2     | # = -                     | 🧆 🗰 🛺      |

| Workspace                                                         | — <b>— </b>         | Objects 💳                | <b>→ → ×</b>          | 🛱 counte | er. vhd                   |            |

| ▼ Instance                                                        | Desigr              | ▼ Name                   |                       | 1n #     |                           |            |

| 🛛 🖂 🗖 counter                                                     | counte              | cour                     | nt                    | 17       | begin                     |            |

| Leo ctr                                                           | counte              | s dk                     |                       | 18       | -                         | input'lo   |

| 🗾 standard                                                        | standa              | 🔷 resel                  |                       | 19       |                           | lt(i) := i |

|                                                                   |                     |                          |                       | 20       | carry                     | 7 := input |

|                                                                   |                     |                          |                       | 21       |                           | when carr  |

| B                                                                 |                     |                          |                       | 22       | end loop                  |            |

|                                                                   |                     |                          | <u>S</u> ignal Declar |          | return m                  | · · · ·    |

|                                                                   |                     |                          | <u>C</u> reate Wave   |          | end increme               | ent;       |

|                                                                   |                     |                          | <u>V</u> iew Memory   | Contents | begin                     |            |

|                                                                   |                     |                          | Insert Breakp         | oint     | etr.                      |            |

|                                                                   |                     |                          | Add to <u>W</u> ave   | : 🕨      | Selected Signals          | reset)     |

| II                                                                |                     |                          | Add to <u>L</u> ist   | ۱.       | Signals in <u>R</u> egion |            |

|                                                                   | ▶                   |                          | L <u>og</u> Signal    | •        | Signals in <u>D</u> esign |            |

| 🕅 Project 🎵 Library 🌆 sim 🗟                                       | Files 🔹             |                          | <u>I</u> oggle Cove   | rage 🕨 🕨 | r.vhd                     | _          |

|                                                                   |                     |                          | Force                 |          | $\vdash$                  |            |

| Transcript                                                        |                     |                          | NoForce               |          |                           |            |

| # // ModelSim SE 6.0 Aug 19 2004                                  | 4                   |                          | Cloc <u>k</u>         |          |                           |            |

|                                                                   |                     |                          |                       |          |                           |            |

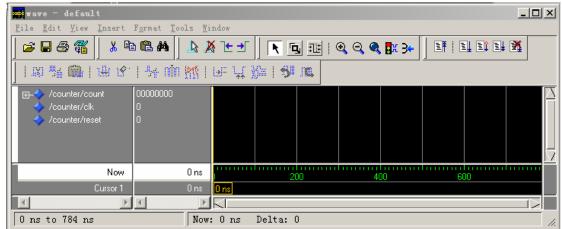

After the selected signals or signals in the whole region are added, a default waveform will appear with the signals on the vertical axis and the time along the horizontal axis as shown below:

If you right click on the signals, you can change the display radix to make it easier to see whether the counter works correctly. Go to Radix, click on *unsigned*.

It is necessary to set values manually for the input since there is no testbench in this case.

Right click the signal *clock*, select clock, define it by setting the parameters:

| MDefine Clock      | x   |

|--------------------|-----|

| Clock Name         | 1   |

| sim:/counter/clock |     |

| offset Duty        | _   |

| 0 50               |     |

| Period Cancel      |     |

| 100                |     |

| Logic Values       |     |

| High: 1 Low: 0     |     |

| First Edge         |     |

| OK Can             | cel |

Other input signals are assigned differently.

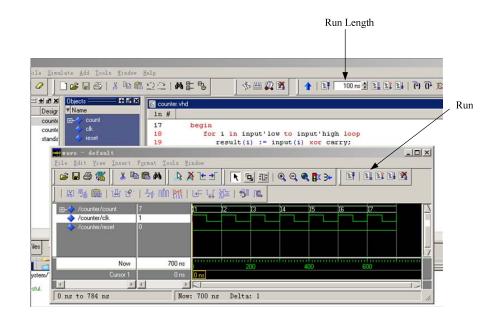

Right click the signal, select *force* and set a specific value in a binary format. Press the *run* button on the toolbar, the waveform looks like the one below:

The wave that you see above is a box with numbers in it. If you change the radix back to binary, when you see 10000, it means that this is a bus (collection of wires) instead of an individual input or output. You can see the individual wires for each bus if you click "⊞" next to each signal.

The simulation duration can be set by entering a value in the Run Length box.

## • Summary

In this tutorial, we have built a project for a counter that is edited and simulated for you to get familiar with ModelSim CAD tool. Neither gate delays nor interconnect delays are considered since it is only a behavioral simulation that gives the least accurate prediction of how the circuit will perform. However, it is very useful during the initial debugging of your design.